Panmnesia Signs Strategic Partnership with Openchip at MWC26

Share

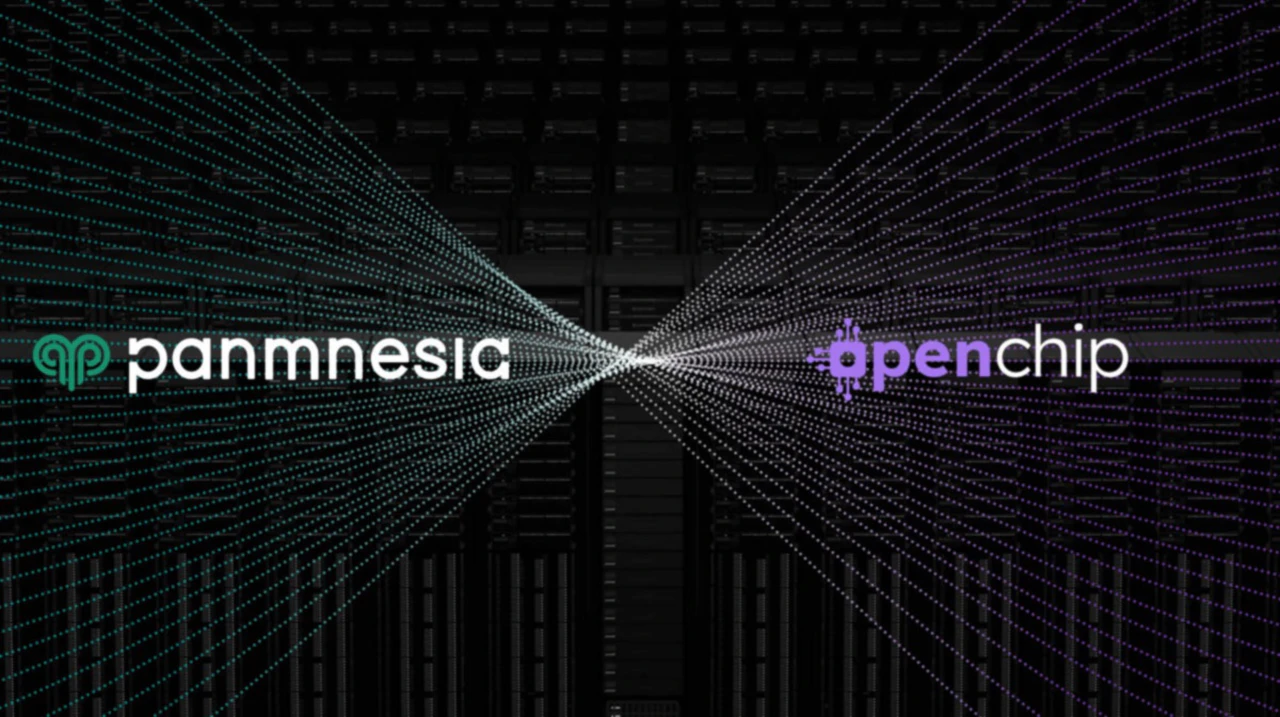

Barcelona, Spain – March 3, 2026 – Panmnesia, a provider of advanced link solutions, announced today that it has signed a Memorandum of Understanding (MOU) with Openchip, a European AI accelerator design company, at MWC26 in Barcelona. The agreement focuses on technical collaboration related to AI/HPC infrastructure.

The agreement marks a step toward technical collaboration aimed at enhancing performance, scalability, and resource efficiency in AI accelerator and infrastructure environments. The two companies exchanged in-depth technical perspectives on link architecture design and system optimization approaches for AI/HPC systems.

As large-scale AI models continue to proliferate, efficient utilization of accelerator resources and high-performance connectivity within data centers have emerged as key competitive factors. In particular, standards-based link technologies that seamlessly connect AI accelerators and infrastructure resources are rapidly gaining industry attention. Under the agreement, the companies are going to explore collaboration opportunities across various link standards and system architecture configurations.

Executive Quote

Myoungsoo Jung, CEO of Panmnesia, said, “As AI accelerator and infrastructure environments evolve rapidly, link technologies are becoming increasingly critical to overall system performance. Through global partnerships, Panmnesia will continue to advance next-generation link technologies for AI infrastructure.”

Cesc Guim, CEO of Openchip, said, “This collaboration is essential for building a scalable and efficient AI infrastructure in the global tech landscape. In our mission to strengthen digital sovereignty through open-standard, high-performance silicon, by combining RISC-V accelerators with Panmnesia’s advanced link technologies, we are tackling the data movement bottlenecks that define the next generation of AI and computing”.

About Openchip

Openchip is a European systems company developing a unique portfolio of RISC-V*–based accelerators, along with full-stack hardware and software infrastructure for next-generation AI and supercomputing applications. Headquartered in Barcelona with a growing presence across Europe, Openchip brings together top-tier talent in silicon engineering and software engineering, with a strong focus on artificial intelligence. Its end-to-end optimized products advance digital sovereignty and deliver best-in-class performance for Europe’s most critical computing needs.

For more information, visit https://openchip.com/.

For more information, please contact: LLYC - [email protected]

*RISC-V: An open processor architecture standard that allows companies to freely design and customize semiconductor chips.

About Panmnesia

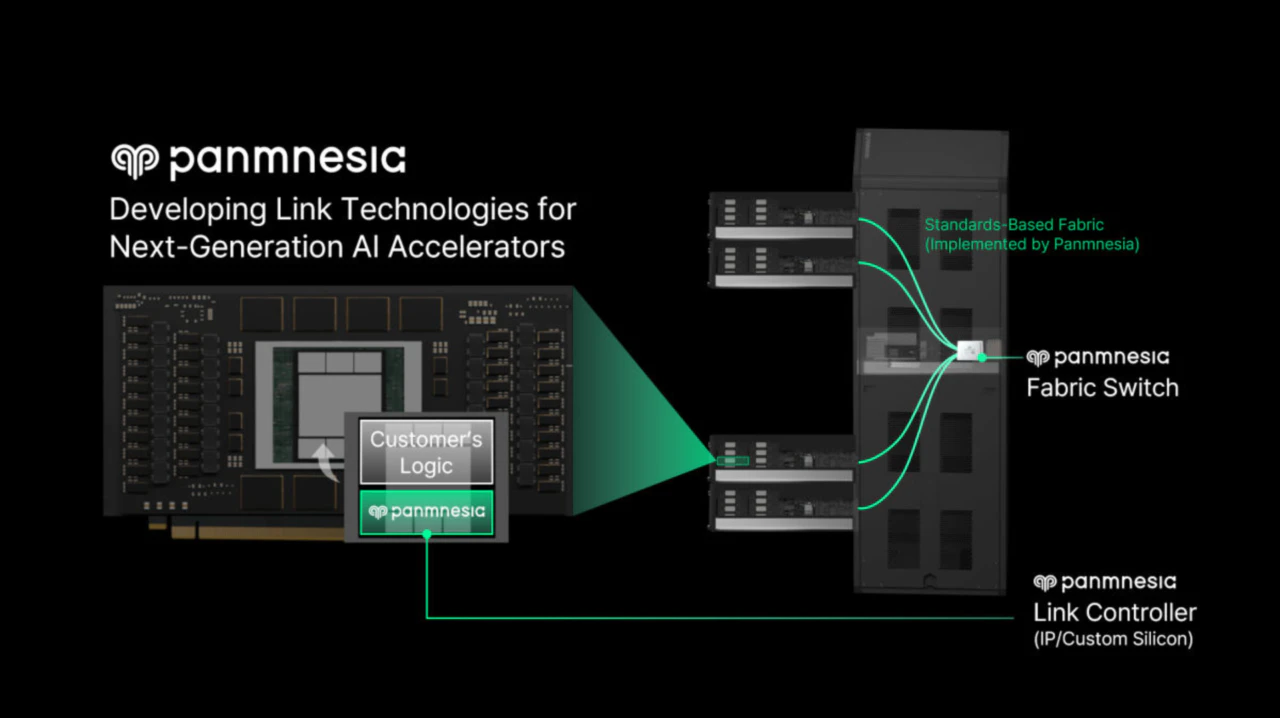

Panmnesia is a company developing advanced link solutions that enhance scalability and resource efficiency in AI infrastructure. The company offers a comprehensive portfolio that includes Link Controllers, Fabric Switches, and Memory Expansion Kits.

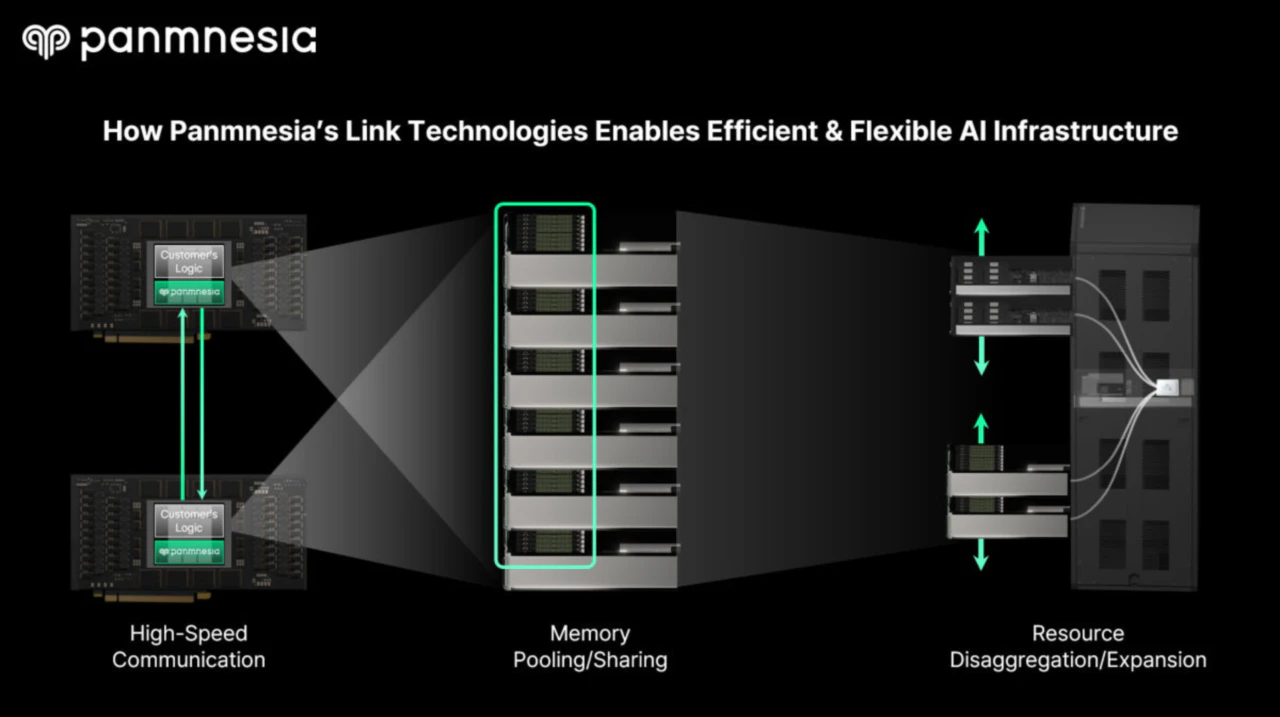

In particular, Panmnesia also serves as a partner providing Custom Silicon solutions based on Link Controller and Switch technologies. These solutions enable semiconductor companies to implement silicon chips optimized for scalable data center environments. Through its technologies, Panmnesia supports high-speed communication between devices, memory pooling and sharing, and resource disaggregation and expansion—allowing diverse system devices to be flexibly/efficiently integrated within large-scale data center architectures.

Recently, the company unveiled its CXL† (Compute Express Link) 3.2 / PCIe 6.4 switch product. To further strengthen its technological competitiveness, Panmnesia has independently designed and validated a reference architecture that enables flexible memory expansion without the need for additional GPU deployment. This technology was recognized for its innovation by receiving CES Innovation Awards for two consecutive years, at CES 2024 and CES 2025.

For more information, visit https://panmnesia.com/.

†CXL (Compute eXpress Link): A high-speed, low-latency interconnect standard that enables organic connection among CPUs, GPUs, and memory, allowing computing resources to be flexibly expanded and utilized as needed.